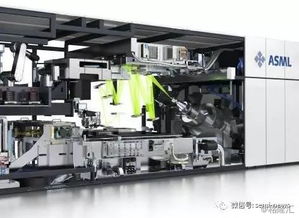

随着摩尔定律演进放缓与异构集成、Chiplet(芯粒)等技术的兴起,集成电路产业正步入一个全新的融合时代。设计复杂度呈指数级增长,异构系统集成了数字、模拟、射频、存储乃至光电子等不同工艺、不同功能的模块,这对传统的集成电路设计流程,特别是测试环节,提出了前所未有的挑战。在这一背景下,打造稳定、高效、智能的自动测试设备(ATE)不仅是保障产品质量与可靠性的基石,更是抓住融合时代机遇、抢占技术制高点的关键。

一、 融合时代的测试新挑战

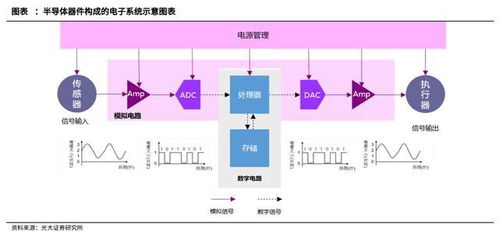

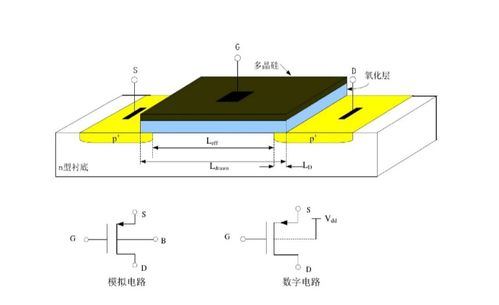

- 设计复杂度与异构性激增:现代SoC(片上系统)集成了数十亿甚至上百亿晶体管,并融合了多种计算单元、加速器和专用IP。测试向量生成、故障覆盖率评估的难度极大提升。混合信号、高速接口(如DDR5/PCIe 6.0)的测试要求精度与时序控制达到前所未有的水平。

- 测试成本与时间压力:测试成本在芯片总成本中的占比日益升高。复杂的测试程序、漫长的测试时间与高昂的ATE设备投资形成了巨大矛盾。如何在保证测试质量的显著压缩测试时间、降低单颗芯片测试成本,成为产业核心痛点。

- 可靠性要求与生命周期管理:在汽车电子、工业控制、数据中心等关键领域,芯片的可靠性与长期稳定性至关重要。测试不再局限于出厂前的功能验证,还需覆盖老化测试、在线监控、失效分析等全生命周期质量保障。

- 数据洪流与智能分析需求:测试过程中产生的海量数据(电参数、时序、温度、良率等)蕴含丰富信息。如何实时采集、高效管理并利用人工智能/机器学习技术进行深度分析,实现预测性维护、测试程序优化和良率提升,是智能化测试的核心。

二、 多维度打造稳定高效的ATE系统

应对上述挑战,需要从硬件、软件、方法学和生态系统多个维度进行系统性创新与协同。

1. 硬件平台:向高精度、高灵活性与高密度演进

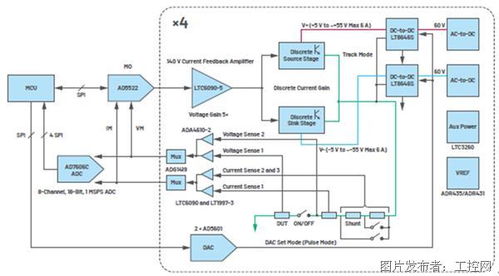

模块化与可扩展架构:采用高度模块化的硬件平台,支持数字、模拟、射频、大功率等不同测试资源的灵活配置与平滑升级,以快速适应不同芯片(尤其是Chiplet)的测试需求。

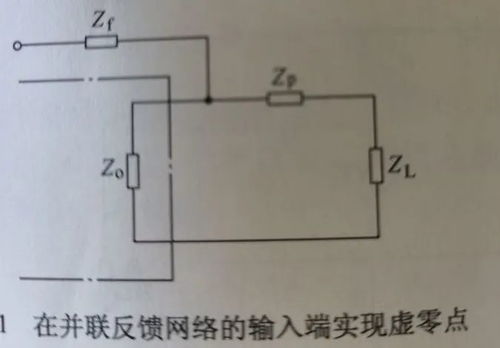

高性能引脚电子与仪器:提升引脚电子的数据速率、时序精度和电压/电流测量范围,满足高速SerDes、高精度数据转换器(ADC/DAC)等接口的严苛测试要求。

并行测试与多站点能力:通过增强数字通道密度、优化资源共享架构,大幅提升并行测试能力(同测数),有效摊薄测试成本。需解决多站点测试下的功耗、散热与信号完整性问题。

集成化与靠近DUT(被测器件):将部分测试功能(如电源管理、简单激励/响应)集成到负载板(Load Board)或探针卡(Probe Card)上,缩短信号路径,提高测试速度与信号保真度。

2. 软件与算法:智能、开放与自动化

智能测试程序生成(TPG):利用AI算法,基于设计仿真数据、历史测试数据自动生成和优化测试向量,在保证故障覆盖率的前提下,大幅压缩测试模式长度。

自适应测试与实时优化:在测试过程中实时分析芯片性能参数,动态调整测试条件(如电压、频率),实现芯片性能分级(Bin Split)或筛选潜在早期失效器件,提升整体产品品质与价值。

开放统一的软件框架:提供标准化API和开发环境,方便用户集成第三方工具、自定义算法和数据分析流程,形成从设计仿真、测试开发到生产数据分析的完整工具链。

大数据分析与良率管理系统:构建集成的数据分析平台,将ATE数据与晶圆制造(WAT/CP)、封装(FT)乃至系统级测试(SLT)数据关联分析,快速定位缺陷根因,驱动设计与工艺改进。

3. 测试方法学创新

基于DFT(可测试性设计)的协同:推动测试工程师与设计工程师的早期协作,采用先进的DFT技术,如IEEE 1687(IJTAG)、内建自测试(BIST)、扫描压缩等,简化ATE测试复杂度,提升测试效率。

系统级测试(SLT)与ATE的融合:针对复杂SoC和异构集成芯片,将部分应用场景下的功能测试(SLT)与ATE的结构化测试相结合,形成互补的测试策略,在成本与覆盖率之间取得最佳平衡。

* 面向Chiplet与先进封装的测试策略:发展KGD(已知合格芯片)测试、中间测试(Interposer/Bridge测试)和最终系统级测试的分层测试方案,确保每个Chiplet和集成后的系统均满足性能与可靠性要求。

4. 构建协同生态系统

产业上下游深度合作:ATE供应商需与EDA工具商、IP提供商、晶圆代工厂、封装测试厂乃至终端系统厂商建立更紧密的伙伴关系,共同定义测试标准,开发联合解决方案。

人才培养与知识共享:培养兼具集成电路设计、测试理论和数据分析能力的复合型人才。通过行业论坛、技术联盟促进知识交流与最佳实践分享。

三、 拥抱机遇,引领未来

集成电路的融合时代,既是挑战的汇聚点,也是创新的催化剂。自动测试设备作为连接设计与制造的“质量守门人”,其角色正从被动验证向主动赋能转变。通过从硬件性能、软件智能、方法学创新到生态协同的多维度入手,打造下一代稳定、高效、智能的ATE系统,我们不仅能有效应对当前复杂芯片的测试难题,更能为即将到来的、由异构集成和Chiplet技术驱动的产业新浪潮奠定坚实基础。唯有如此,整个集成电路产业才能在融合时代的机遇与挑战中行稳致远,持续引领信息技术的革命性进步。