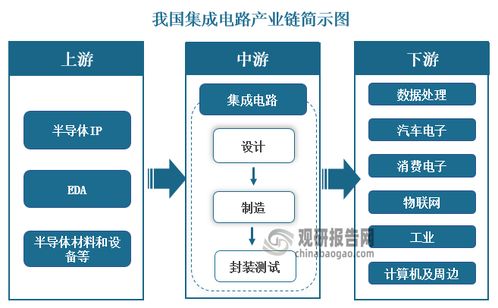

模拟集成电路(Analog IC)设计是现代电子系统的核心,它将抽象的电路概念转化为物理硅片上的复杂结构。这一过程遵循一个严谨而迭代的设计流程,而版图设计则是连接电路原理与物理实现的关键桥梁。本文将概述模拟集成电路的标准设计流程,并深入探讨版图设计的基础知识。

一、模拟集成电路设计流程

模拟集成电路设计是一个自上而下(Top-Down)与自下而上(Bottom-Up)相结合的系统工程,通常包含以下几个主要阶段:

- 系统定义与规格制定:明确芯片的功能、性能指标(如增益、带宽、功耗、噪声)、工作环境以及封装形式。这是所有后续设计的蓝图。

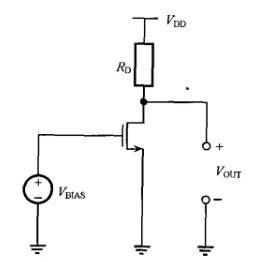

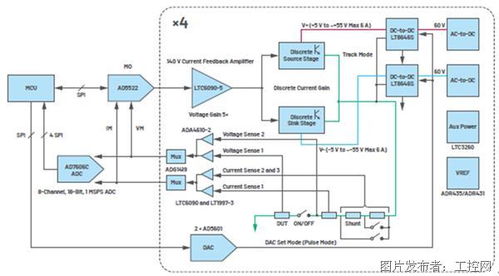

- 架构设计与电路设计:根据规格,选择合适的电路架构(如运算放大器、锁相环、数据转换器等)。随后进行晶体管级的电路设计,使用SPICE等仿真工具验证电路的直流、交流、瞬态等特性,确保其满足理论性能要求。

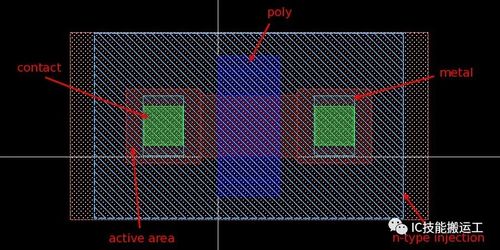

- 版图设计:将经过验证的电路原理图转化为一系列几何图形(版图),这些图形定义了制造过程中各层材料(如多晶硅、金属、扩散区)的形状、尺寸和相对位置。这是物理实现的第一步,其质量直接决定芯片的性能、可靠性和制造成本。

- 物理验证:对生成的版图进行严格的检查,主要包括:

- 设计规则检查(DRC):确保版图符合芯片制造厂(Foundry)的工艺加工极限规则,如最小线宽、最小间距等。

- 电路图与版图一致性检查(LVS):确认版图所代表的电路连接关系与原始电路原理图完全一致,避免连接错误。

- 寄生参数提取(PEX):从版图中提取导线电阻、寄生电容等非理想寄生参数,生成包含这些寄生效应的新网表。

- 后仿真:将提取出的寄生参数反标回电路仿真模型,进行带寄生效应的电路仿真。这是评估版图对电路性能(如速度、功耗、噪声)影响的关键步骤,通常需要根据结果反复优化版图。

- 流片与测试:将所有最终确认的版图数据(通常为GDSII格式)提交给芯片制造厂进行生产(即“流片”)。芯片制造完成后,在测试台上对样片进行全面的功能和性能测试,验证其是否达到设计规格。

二、版图设计基础

版图设计是艺术与技术的结合,其核心目标是在满足所有物理和电气约束的前提下,实现最优的性能、面积和可靠性。以下是几个基础而关键的概念:

- 工艺层与设计规则:芯片制造工艺定义了多种材料层(如N阱、有源区、多晶硅、金属层、接触孔、通孔)。每一层都有严格的设计规则,版图设计必须绝对遵守这些规则,否则会导致制造失败或性能缺陷。

- 匹配性设计:对于差分对、电流镜等对器件对称性要求极高的电路,版图必须采用精密匹配的布局技巧,如共质心结构、交叉耦合、添加虚拟器件等,以抵消工艺梯度带来的失配,确保电路精度。

- 噪声隔离与抑制:模拟电路对噪声(特别是衬底噪声和电源噪声)极为敏感。版图设计中需采用保护环、隔离阱、独立的电源/地线、合理的布线策略(如信号线与噪声线隔离、采用屏蔽线)等手段来最小化噪声干扰。

- 寄生效应控制:寄生电阻和电容会降低电路速度、增加功耗、引起信号串扰。通过使用更宽的导线(减小电阻)、增大敏感节点间距(减小耦合电容)、优化布线走向等方法,可以有效地控制寄生效应。

- 可靠性考虑:包括电迁移(大电流导线需足够宽)、天线效应(防止工艺中电荷积累损坏栅氧)、闩锁效应(通过合理的阱和衬底接触布局来预防)等。

- 面积优化:在满足性能和可靠性要求的基础上,紧凑的布局可以降低芯片成本。这需要对器件布局、布线通道进行精心规划。

结论

模拟集成电路的设计流程是一个环环相扣、反复迭代的精密过程。其中,版图设计绝非简单的“画图”,而是将电路性能、制造工艺和物理现实深度融合的创造性工作。扎实的版图设计基础——深刻理解工艺规则、匹配原理、寄生效应和噪声机制——是设计出高性能、高可靠性模拟芯片的基石。随着工艺节点的不断进步,版图设计面临的挑战也日益增加,其重要性在集成电路设计领域中愈发凸显。